您现在的位置是:主页 > USB3.2超高速协议规范 >

USB3.2 GEN2超高速链路初始化和训练

发布时间:2022-12-30 11:43:13所属栏目:USB3.2超高速协议规范 已帮助人编辑作者:【USB接口百科】

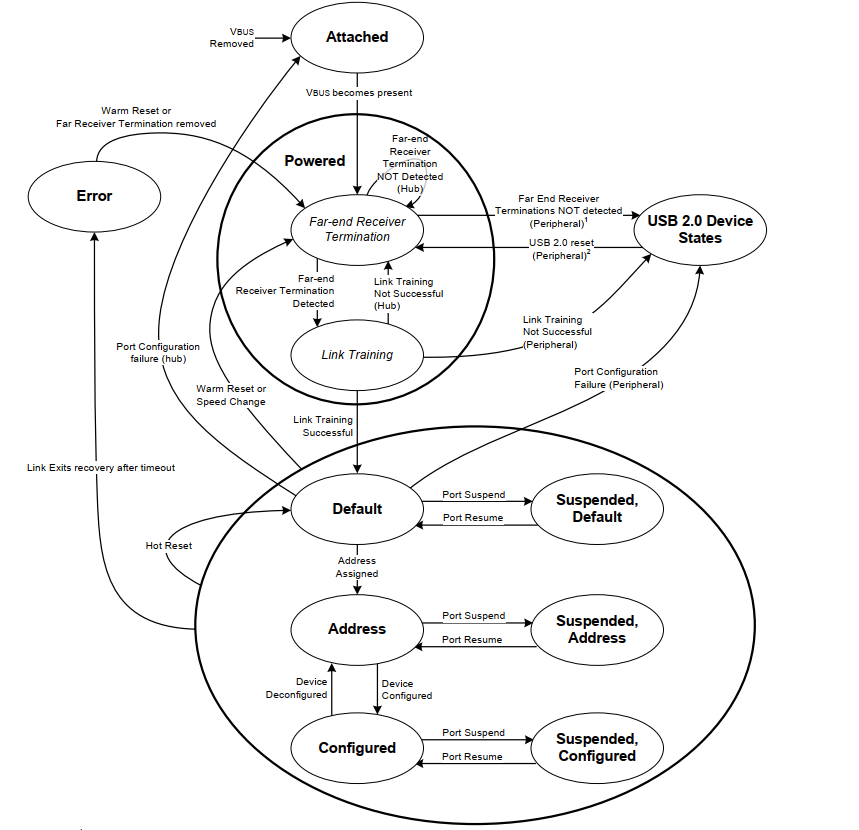

GEN2的链路初始化和训练和GEN1为似,基主要操作如下:

配置和初始化链路位锁和符号锁Rx均衡训练LAN的极性反转块对齐(Block alignment)训练序列由用于初始化位对齐、符号对齐、块对齐和优化均衡的有序集组成。

USB3.2 GEN2相对于GEN1多了一个块对齐。

位锁定是指时钟/数据恢复 (CDR) 电路从传入数据流中提取相位和频率信息的能力。 位锁定是通过发送足够长的位序列(包含交替的 0 和 1 的 D10.2 符号)来实现的,因此 CDR 将时钟大致集中在位内。

USB3.2 GEN2链路的训练规则USB3.2 GEN2的位锁和USB3.2 GEN1的位锁念相同。

训练序列由用于初始化位对齐、符号对齐、块对齐、扰频同步和接收器均衡的有序集组成。规则如下:

训练序列有序集应包含 16 个符号并采用 128b/132b 编码。TSEQ、TS1 或TS2 有序集的传输只能被SKP 有序集或SYNC 有序集中断。在GEN2训练期间,每 16384 个 TSEQ 集应传输一个 SYNC 有序集。当发送 TS1 或 TS2 有序集时(在恢复、轮询.活动、恢复.配置、热复位和轮询.配置期间),应在 Gen 2 操作中每 32 个有序集发送一个 SYNC 有序集。TSEQ 训练序列被传输 524,288 次以允许测试许多系数设置。

对于 TSEQ、TS1 和 TS2 有序集,发射器需要跟踪在线传输的位(加扰后)的运行 DC 平衡。 运行中的 DC Balance 是传输的 1 数量和传输的 0 数量之间的差值。

PHY 应能够在任一方向跟踪至少 511 位的差异:511 个 1 比 0 多,511 个 0 比 1 多。 使用的任何计数器应在其限制(而非翻转)处饱和,并在达到其限制后继续跟踪减少。 例如,一个可以跟踪511位差异的计数器,如果检测到513的差异,就会在511饱和,如果以后差异减少2,则变为509。

在 Gen 2 数据块传输开始时,运行的 DC Balance 设置为 0.

对于传输的每个 TSEQ、TS1 或 TS2 有序集,发射机应评估运行的 DC 平衡并传输为符号 14 和 15 定义的 DC 平衡符号之一,如下面的算法定义。 如果需要减少 1 的数量,则传输 DC 平衡符号 20h(对于符号 14)和 08h(对于符号 15)。 如果需要减少 0 的数量,则发送 DC 平衡符号 DFh(对于符号 14)和 F7h(对于符号 15)。 如果不需要更改,则传输适当的 TS 标识符符号。 为符号 14 或 15 传输的任何 DC 平衡符号绕过加扰,而 TS 标识符符号遵循标准加扰规则。 应使用以下算法来控制 DC 平衡:

如果在 TS 有序集的符号 11 的末尾运行, DC 平衡器 > 31,则传输符号 14 的 DFh 和符号 15 的 F7h 以减少 0 的数量,或传输符号 14 的 20h 和符号 15 的 08h 以减少 1s 的数量。否则,如果在 TS 有序集的符号 11 末尾运行, DC平衡器 > 15,则为符号 15 发送 F7h 以减少 0 的数量,或为符号 15 发送 08h 以减少 1 的数量。 传输符号 14 的正常 TS 标识符符号(加扰)。否则,为符号 14 和 15 传输正常的 TS 标识符符号(加扰)。在确定 TS 有序集是否有效时,接收器可以检查符号 14 和 15 的以下值: 解扰后的适当 TS 标识符符号,或符号 14 解扰前的 DFh 或 20h 的有效 DC 平衡符号, 或 F7h 或 08h 的有效 DC 平衡符号,然后为符号 15 解扰。

Gen 2 操作所需的新有序集是数据流起始 (SDS) 有序集。 这仅针对 Gen 2 操作定义,没有 Gen 1 对应项。 它应在 Polling.Idle、Recovery.Idle 和 Hot Reset.Exit 期间传输以定义转换从有序集块到数据流。 它不得在任何其他时间传输。当不处于环回状态时,跟在 SDS 有序集之后的块应该是一个数据块,并且该数据块的第一个符号是数据流的第一个符号。

#USB3.2 Gen 2 TS1 Ordered Set| Symbol Number | Symbol | Description |

|---|---|---|

| 0-3 | 1Eh | TS1 Identifier |

| 4 | 00h | Reserved for future use |

| 5 | 见Gen 1/Gen 2 Link Configuration表 | Link Functionality |

| 6-13 | 1Eh | TS1 Identifier |

| 14-15 | TS1 Identifier (1Eh) or a DC Balance Symbol | TS1 Identifier or DC balance |

| Symbol | Number | Symbol Description |

|---|---|---|

| 0-3 | 2Dh | TS2 Identifier |

| 4 | 00h | Reserved for future use |

| 5 | 见Gen 1/Gen 2 Link Configuration表 | Link Functionality |

| 6-13 | 2Dh | TS2 Identifier |

| 14-15 | TS2 Identifier (2Dh) or a DC Balance Symbol | TS2 Identifier or DC balance |

| Symbol Number | Symbol Description | |

|---|---|---|

| 0,2,4,6,8,10,12,14 | 00h | Symbol 0 SYNC identifier |

| 1,3,5,7,9,11,13,15 | FFh |

| Symbol Number | Symbol | Description |

|---|---|---|

| 0 through 3 | E1h | SDS Ordered Set Identifier |

4 through 15 |55h| Body of SDS Ordered Set

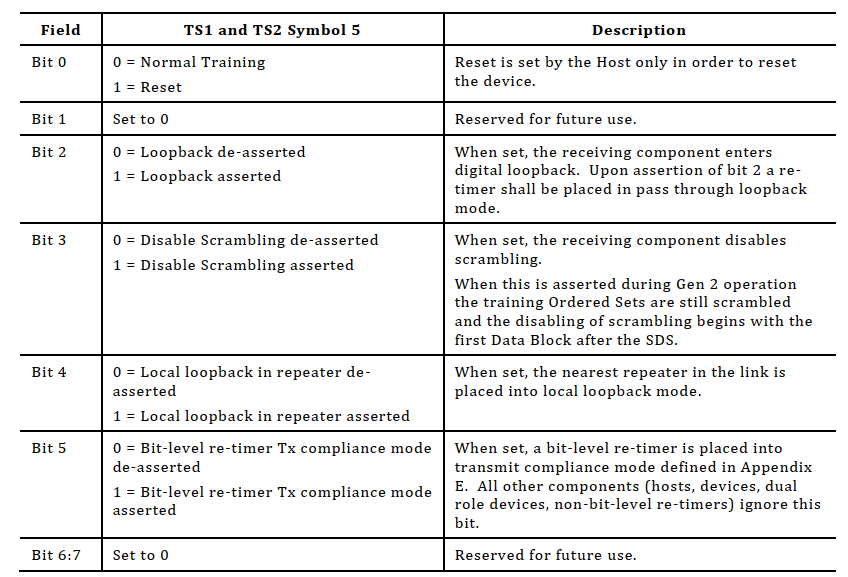

USB3.2 GEN2 训练控制位训练控制位位于 TS1 和 TS2 有序集中的链路功能符号中。

链路配置字段的位 0 和位 2 不应同时设置为 1。 如果接收器在接收到的链路配置字段中检测到这种情况,则应忽略所有训练控制位。

在链路训练期间,SYNC 块的 132 位是一个唯一的位模式,接收器使用它来确定接收到的位流中块头的位置。 从概念上讲,接收器可以处于块对齐的三个不同阶段:未对齐、对齐和锁定。 定义这些阶段是为了说明所需的行为,但并不意味着指定所需的实现。

未对齐阶段:接收器在退出低功耗链路状态时或在定向时进入此阶段。 在此阶段,接收器监控 SYNC OS 接收到的比特流。 当检测到一个时,它们调整与它的对齐并进行对齐阶段。对齐阶段:在此阶段,接收器监视接收到的比特流以获取同步有序集。 如果检测到 SYNC OS 的对齐方式与当前对齐方式不匹配,则接收器应将其对齐方式调整为新接收的 SYNC OS。 收到 SDS OS 后,接收器将进入锁定阶段。 如果接收到未定义的块头,则允许接收器返回到未对齐阶段。 当接收 SKP 订购的长度集不是 16 时,接收器应根据需要在此阶段调整对齐符号。

对齐阶段:在此阶段,接收器会监视接收到的 SYNC 有序集的比特流。 如果检测到 SYNC OS 的对齐方式与当前对齐方式不匹配,则接收器应将其对齐方式调整为新接收的 SYNC OS。 收到 SDS OS 后,接收器将进入锁定阶段。 如果接收到未定义的块首标,则允许接收器返回到未对齐阶段。 当接收 16 个符号以外的 SKP 有序长度集时,接收器应根据需要调整此阶段的对齐。

锁定阶段:接收器在此阶段不应调整其块对齐。 数据块预计会以给定的对齐方式接收,调整块对齐方式会干扰这些块的处理。 如果接收到未定义的块头,接收器应返回到未对齐或对齐阶段。 当接收 16 个符号以外的 SKP 有序长度集时,接收器应根据需要调整此阶段的对齐。

在进入 U1 时,发射器可能会在断电之前发送非预期数据。 这些位没有意义,可能是由于在发送器内部并行数据路径中间结束的块边界而出现的.

以上就是USB接口百科为您提供USB3.2 GEN2超高速链路初始化和训练的解读,本文章链接: http://www.usb-hub.cn/usb32gf/42241.html 欢迎分享转载,更多婚礼相关资讯请前往USB3.2超高速协议规范

相关文章

猜你喜欢

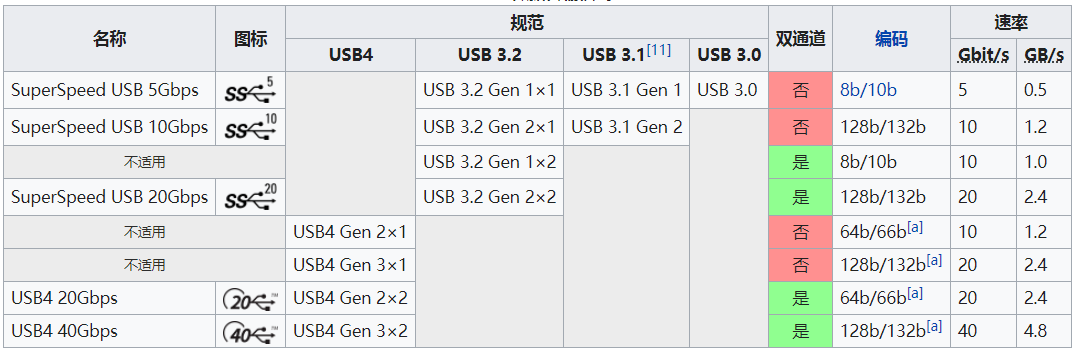

USB超高速3.0/3.2在电磁、引脚定义及物理接口TYPE-C上的变化

USB 3.0,其USB速率模式称为“Super Speed”,是通用序列总线(Universal Serial Bus,...

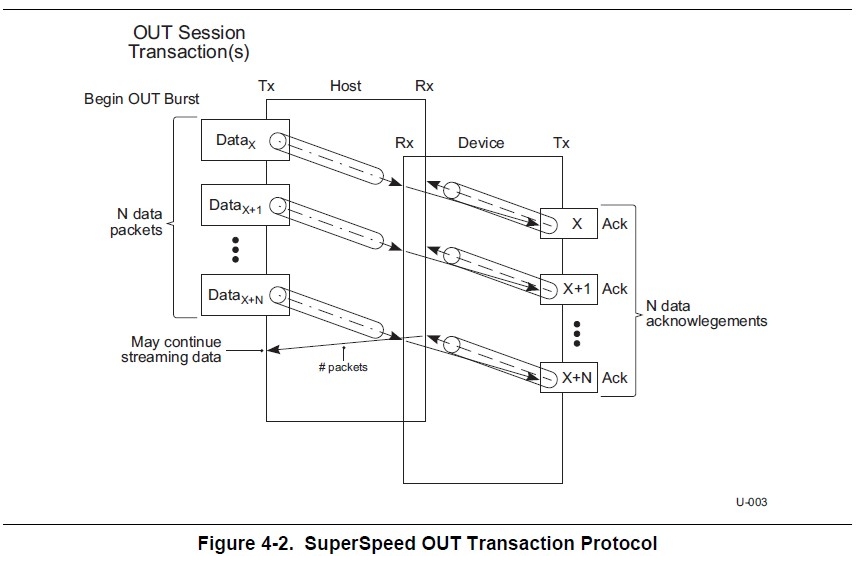

USB超高速3.0协议与USB2.0协议的差异

超高速在框架层级是向后兼容 USB 2.0 的。然而, USB 2.0 和超高速协议还是有一...

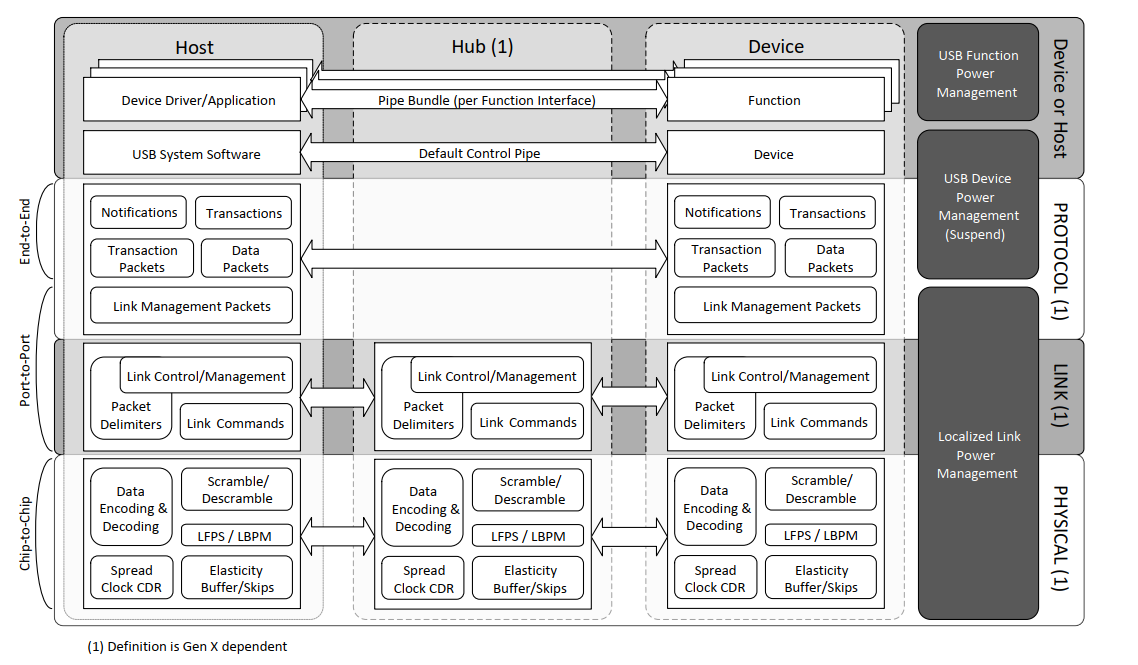

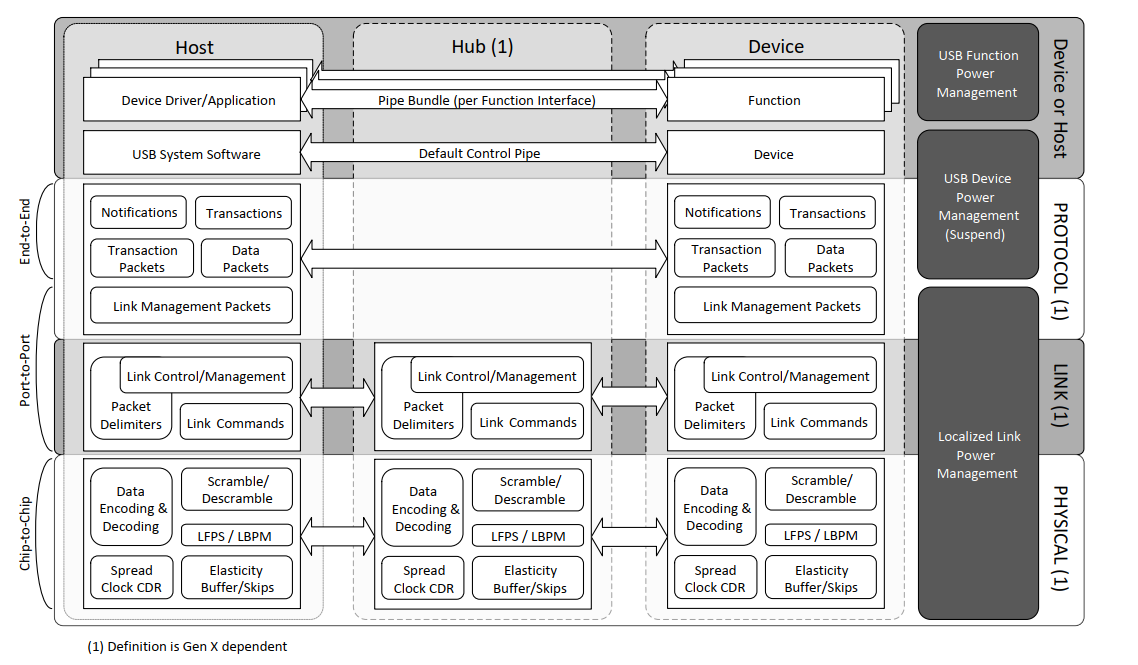

USB超高速(SuperSpeed)体系结构

USB超高速(SuperSpeed)体系结构在协议层分为物理层,数据链路层,协议层。...

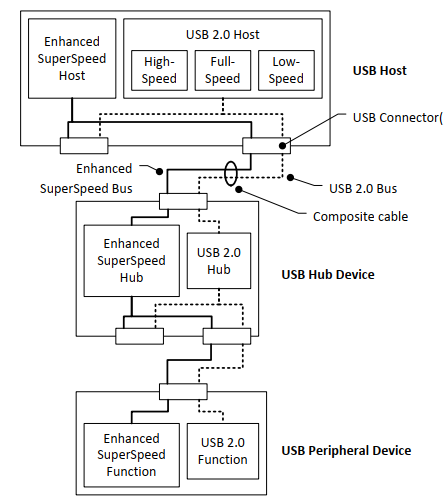

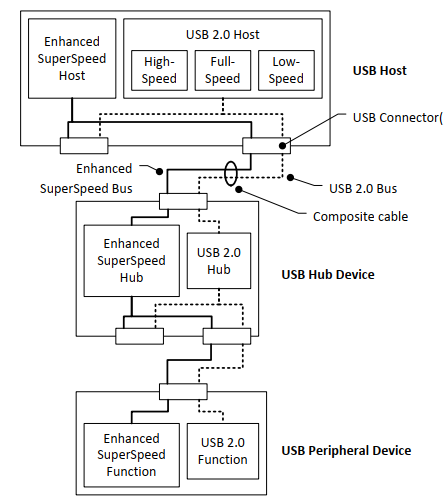

USB3.2超高速兼容USB2.0数据收发的双总线架构

超高速USB体系和以前的USB版本的功能一致,都是通过USB线缆将USB主机USB外设相...

USB接口百科推荐

USB超高速 配置概要描述符

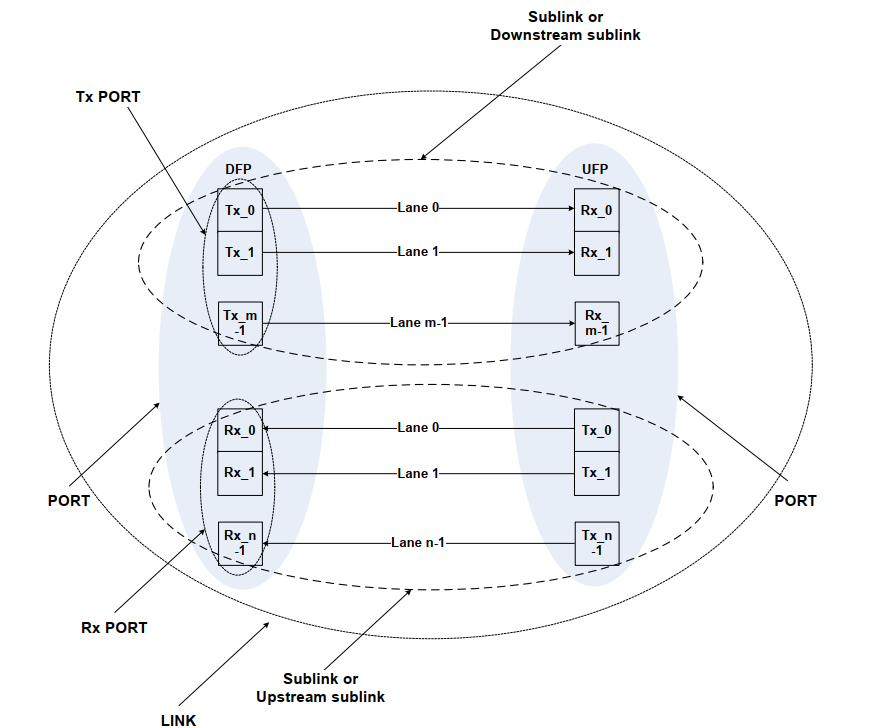

USB3.2中数据通路lan的概念

USB3.2超高速链路通道极性反转

USB超高速设备描述符的bMaxPacketSize0为0x09

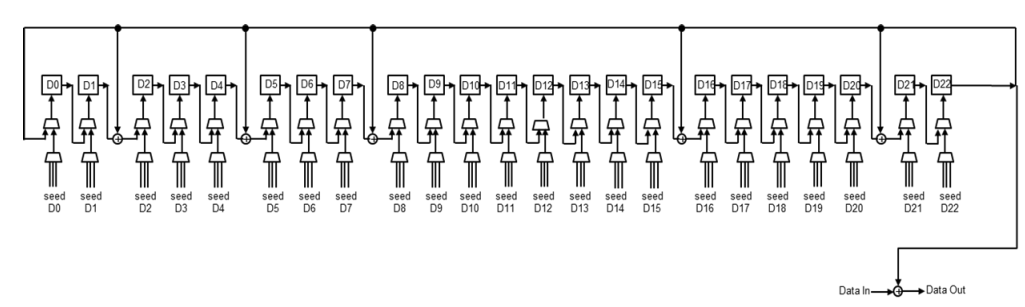

USB3.2超高速GEN2数据扰频

USB超高速(SuperSpeed)体系结构

USB3.2超高速兼容USB2.0数据收发的双总线架构

USB3.2超高速的设备总线枚举

USB超高速规范物理层概述

USB3.2超高速 USB2.0扩展特性描述符

USB3.2超高速 BOS描述符

USB超高速 增强型超高速USB设备特性描述符

USB超高速 GEN1设备状态

USB3.2时钟补偿-弹性缓冲器和SKP有序集

USB3.2超高速描述符分类